# **KNX RW sI**

# Niederschlags- und Windsensor

Artikelnummer 70162

**Installation und Einstellung**

| 1.   | Sicherheits- und Gebrauchshinweise                | . 3 |

|------|---------------------------------------------------|-----|

| 2.   | Beschreibung                                      | . 3 |

| 3.   | Installation und Inbetriebnahme                   |     |

| 3.1. | Montageort                                        | . 4 |

| 3.2. | Position der Sensoren                             | . 6 |

| 3.3. | Montage des Sensors                               | . 6 |

|      | 3.3.1. Halterung anbringen                        | . 6 |

|      | 3.3.2. Gerät anbringen und anschließen            | . 7 |

| 3.4. | Hinweise zur Montage und Inbetriebnahme           | . 8 |

| 4.   | Gerät adressieren                                 | 8   |

| 5.   | Übertragungsprotokoll                             | 10  |

| 5.1. | Liste aller Kommunikationsobjekte                 |     |

| 6.   | Einstellung der Parameter                         | 15  |

|      | 6.0.1. Verhalten bei Spannungsausfall/-wiederkehr | 15  |

|      | 6.0.2. Speicherung von Grenzwerten                | 15  |

|      | 6.0.3. Störobjekte                                | 15  |

| 6.1. | Allgemeine Einstellungen                          | 15  |

| 6.2. | Regen                                             | 16  |

|      | Wind-Messwert                                     |     |

| 6.4. | Wind-Grenzwerte                                   | 18  |

|      | 6.4.1. Wind-Grenzwert 1-4                         | 18  |

| 6.5. | Berechner                                         | 20  |

|      | 6.5.1. Berechner 1-8                              | 20  |

| 6.6. | Logik                                             | 24  |

|      | 6.6.1. UND Logik 1-8 und ODER Logik 1-8           | 24  |

|      | 6.6.2. Verknüpfungseingänge der UND Logik         | 26  |

|      | 6.6.3. Verknüpfungseingänge der ODER Logik        | 28  |

Dieses Handbuch unterliegt Änderungen und wird an neuere Software-Versionen angepasst. Den Änderungsstand (Software-Version und Datum) finden Sie in der Fußzeile des Inhaltsverzeichnis.

Wenn Sie ein Gerät mit einer neueren Software-Version haben, schauen Sie bitte auf **www.elsner-elektronik.de** im Menübereich "Service", ob eine aktuellere Handbuch-Version verfügbar ist.

### Zeichenerklärungen für dieses Handbuch

$\triangle$

Sicherheitshinweis

4

Sicherheitshinweis für das Arbeiten an elektrischen Anschlüssen,

Bauteilen etc.

**GEFAHR!** ... weist auf eine unmittelbar gefährliche Situation hin, die zum Tod

oder zu schweren Verletzungen führt, wenn sie nicht gemieden

wird.

**WARNUNG!** ... weist auf eine möglicherweise gefährliche Situation hin, die zum

Tod oder zu schweren Verletzungen führen kann, wenn sie nicht

gemieden wird.

**VORSICHT!** ... weist auf eine möglicherweise gefährliche Situation hin, die zu

geringfügigen oder leichten Verletzungen führen kann, wenn sie

nicht gemieden wird.

ACHTUNG!

... weist auf eine Situation hin, die zu Sachschäden führen kann,

wenn sie nicht gemieden wird.

TS In den ETS-Tabellen sind die Voreinstellungen der Parameter durch

eine Unterstreichung gekennzeichnet.

# 1. Sicherheits- und Gebrauchshinweise

Installation, Prüfung, Inbetriebnahme und Fehlerbehebung dürfen nur von einer autorisierten Elektrofachkraft durchgeführt werden.

### VORSICHT! Elektrische Spannung!

Im Innern des Geräts befinden sich ungeschützte spannungsführende Teile.

- Untersuchen Sie das Gerät vor der Installation auf Beschädigungen. Nehmen Sie nur unbeschädigte Geräte in Betrieb.

- Halten Sie die vor Ort geltenden Richtlinien, Vorschriften und Bestimmungen für die elektrische Installation ein.

- Nehmen Sie das Gerät bzw. die Anlage unverzüglich außer Betrieb und sichern Sie sie gegen unbeabsichtigtes Einschalten, wenn ein gefahrloser Betrieb nicht mehr gewährleistet ist.

Verwenden Sie das Gerät ausschließlich für die Gebäudeautomation und beachten Sie die Gebrauchsanleitung. Unsachgemäße Verwendung, Änderungen am Gerät oder das Nichtbeachten der Bedienungsanleitung führen zum Erlöschen der Gewährleistungs- oder Garantieansprüche.

Betreiben Sie das Gerät nur als ortsfeste Installation, das heißt nur in montiertem Zustand und nach Abschluss aller Installations- und Inbetriebnahmearbeiten und nur im dafür vorgesehenen Umfeld.

Für Änderungen der Normen und Standards nach Erscheinen der Bedienungsanleitung ist Elsner Elektronik nicht haftbar.

Informationen zur Wartung, Entsorgung, zum Lieferumfang und den technischen Daten finden Sie in der Installationsanleitung.

# 2. Beschreibung

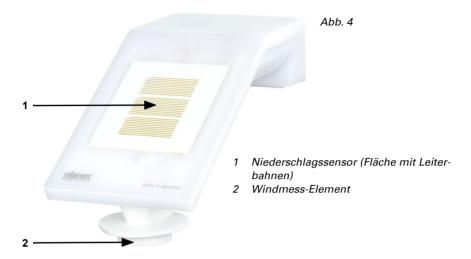

Der **Niederschlags- und Windsensor KNX RW sI** für das KNX-Gebäudebus-System misst die Windgeschwindigkeit und erkennt Niederschlag.

Der Windwert kann zur Steuerung grenzwertabhängiger Schaltausgänge verwendet werden. Über UND-Logik-Gatter und ODER-Logik-Gatter lassen sich die Zustände verknüpfen. Multifunktions-Module verändern Eingangsdaten bei Bedarf durch Berechnungen, Abfrage einer Bedingung oder Wandlung des Datenpunkttyps.

Im kompakten Gehäuse des **KNX RW sI** sind Sensorik, Auswerteelektronik und die Elektronik der Bus-Ankopplung untergebracht.

#### Funktionen:

Windmessung: Die Windstärkemessung erfolgt elektronisch und somit geräuschlos und zuverlässig, auch bei Hagel, Schnee und Minustemperaturen. Auch Luftverwirbelungen und aufsteigende Winde im Bereich des Geräts werden erfasst

- Windsensor-Überwachung: Verändert sich der Windmesswert innerhalb von 48 Stunden um weniger als ± 0,5 m/s, dann wird als Störungsmeldung der maximale Messwert von 35 m/s ausgegeben. Alle Windalarme mit einem Grenzwert unterhalb 35 m/s werden dadurch aktiv

- Niederschlagserkennung: Die Sensorfläche ist beheizt, so dass nur Tropfen und Flocken als Niederschlag erkannt werden, nicht aber Nebel oder Tau. Hört es auf zu regnen oder zu schneien, ist der Sensor schnell wieder trocken und die Niederschlagsmeldung endet

- Schaltausgänge für alle gemessenen und errechneten Werte. Grenzwerte einstellbar per Parameter oder über Kommunikationsobjekte

- 8 UND- und 8 ODER-Logik-Gatter mit je 4 Eingängen. Als Eingänge für die Logik-Gatter können sämtliche Schalt-Ereignisse sowie 16 Logikeingänge in Form von Kommunikationsobjekten genutzt werden. Der Ausgang jedes Gatters kann wahlweise als 1 Bit oder 2 x 8 Bit konfiguriert werden

- 8 Multifunktions-Module (Berechner) zur Veränderung von Eingangsdaten durch Berechnungen, durch Abfrage einer Bedingung oder durch Wandlung des Datenpunkttyps

# 3. Installation und Inbetriebnahme

# 3.1. Montageort

Wählen Sie eine Montageposition am Gebäude, wo Wind und Regen ungehindert von den Sensoren erfasst werden können. Es dürfen keine Konstruktionsteile über dem Gerät angebracht sein, von denen noch Wasser auf den Niederschlagssensor tropfen kann, nachdem es bereits aufgehört hat zu regnen oder zu schneien.

Um das Gerät herum muss mindestens 60 cm Freiraum belassen werden. Dadurch wird eine korrekte Windmessung ohne Luftverwirbelungen ermöglicht. Zugleich verhindert der Abstand, dass Spritzwasser (abprallende Regentropfen) oder Schnee (Einschneien) die Messung beeinträchtigt. Der Windsensor darf nicht mit Wasser in Kontakt kommen. Auch Vogelbiss wird vorgebeugt.

Die Montageposition muss so gewählt werden, dass die Sensoren für Regen und Wind nicht von Personen berührt werden können.

Achten Sie darauf, dass eine ausgefahrene Markise das Gerät nicht in den Windschatten legt.

Abb. 1

Das Gerät muss unterhalb, seitlich und frontal mindestens 60 cm Abstand zu anderen

Elementen (Baukörper, Konstruktionsteile usw.) haben.

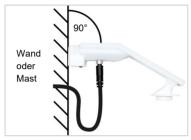

Abb. 2 Das Gerät muss an einer senkrechten Wand (bzw. einem Mast) angebracht werden.

Legen Sie die Zuleitung in eine Schlaufe, bevor Sie sie in Wand oder Anschlussbox führen. So kann Regen abtropfen und rinnt nicht in die Wand oder die Box.

Abb. 3

Das Gerät muss in der Querrichtung horizontal (waagerecht) montiert sein.

### 3.2. Position der Sensoren

#### **ACHTUNG!**

Empfindlicher Windsensor.

- Transportschutz-Aufkleber nach der Montage entfernen.

- Den Sensor am Windmesselement (unten, versenkt) nicht berühren.

# 3.3. Montage des Sensors

# 3.3.1. Halterung anbringen

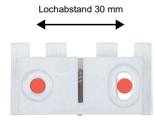

Montieren Sie nun zunächst die Halterung für die Wand- oder Mastmontage. Lösen Sie dazu die Verschraubung der Halterung mit einem Kreuzschlitz-Schraubendreher.

### Wandmontage

### Abb. 5 Ansicht von vorne

Schrauben Sie die Halterung mit zwei Schrauben an die Wand. Verwenden Sie Befestigungsmaterial (Dübel, Schrauben), das für den Untergrund geeignet ist.

Achten Sie darauf, dass die Pfeile nach oben weisen.

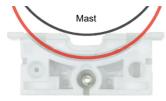

### Mastmontage

Das Gerät wird mit der beiliegenden Schelle am Mast montiert.

Abb. 6 Ansicht von unten

Führen Sie die Schelle durch die Aussparung in der Halterung. Ziehen Sie die Schelle am Mast fest

Achten Sie darauf, dass die Pfeile nach oben weisen.

## 3.3.2. Gerät anbringen und anschließen

Abb. 7

- 1. Schieben Sie das Gerät von oben auf die Halterung.

- 2. Ziehen Sie die Schraube der Halterung an, um das Gerät zu sichern.

- Verschrauben Sie den M8-Steckverbinder des Anschlusskabels mit der Anschluss buchse an der Geräteunterseite.

Verbinden Sie das lose Ende des Anschlusskabels mit KNX-Bus und Hilfsspannung. Nutzen Sie dazu die mitgelieferte Anschlussdose und die Klemmen.

| KNX-Bus:  | Hilfsspannung: |

|-----------|----------------|

| + Rot     | + Gelb         |

| - Schwarz | - Weiß         |

Abb. 8

Entfernen Sie nach der

Montage den Schutzaufkleber am Windsensor

und den Hinweisaufkleber "Abstand" an der

Oberseite des Deckels.

# 3.4. Hinweise zur Montage und Inbetriebnahme

Der Windmesswert und somit auch alle Wind-Schaltausgänge können erst ca. 35 Sekunden nach Anlegen der Versorgungsspannung ausgegeben werden.

Die Konfiguration erfolgt mit der KNX-Software ETS. Die **Produktdatei** steht auf der Homepage von Elsner Elektronik unter **www.elsner-elektronik.de** im Menübereich "Service" zum Download bereit.

Nach dem Anlegen der Busspannung befindet sich das Gerät ca. 4 Sekunden lang in der Initialisierungsphase. In dieser Zeit kann keine Information über den Bus empfangen oder gesendet werden.

## 4. Gerät adressieren

Das Gerät wird mit der Bus-Adresse 15.15.255 ausgeliefert. Eine andere Adresse kann in der ETS durch Überschreiben der Adresse 15.15.255 programmiert werden oder über den Programmier-Taster eingelernt werden.

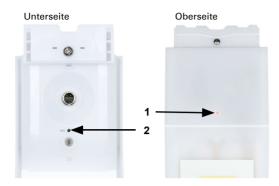

Der Programmier-Taster ist über die Öffnung an der Gehäuseunterseite erreichbar und ca. 15 mm versenkt. Verwenden Sie einen dünnen Gegenstand, um den Taster zu erreichen, z. B. einen Draht 1,5 mm².

### Abb. 9

- 1 Programmier-LED (unter dem semitransparenten Deckel)

- 2 Programmier-Taster zum Einlernen des Geräts

# 5. Übertragungsprotokoll

### Einheiten:

Wind in Meter pro Sekunde

# 5.1. Liste aller Kommunikationsobjekte

### Abkürzungen Flags:

- K Kommunikation

- L Lesen

- S Schreiben

- Ü Übertragen

- A Aktualisieren

| Nr. | Text                                          | Funktion             | Flags | DPT Typ                                        | Größe   |

|-----|-----------------------------------------------|----------------------|-------|------------------------------------------------|---------|

| 1   | Softwareversion                               | Ausgang              | L-KÜ  | [217.1] DPT_Version                            | 2 Bytes |

| 34  | Regen: Schaltausgang                          | Ausgang              | L-KÜ  | [1.1] DPT_Switch                               | 1 Bit   |

| 35  | Regen: Schaltausgang mit festen Verzögerungen | Ausgang              | L-KÜ  | [1.1] DPT_Switch                               | 1 Bit   |

| 36  | Regen: Schaltverzögerung auf Regen            | Eingang              | -SK-  | [7.005] DPT_TimePeriodSec                      | 2 Bytes |

| 37  | Regen: Schaltverzögerung auf kein<br>Regen    | Eingang              | -SK-  | [7.005] DPT_TimePeriodSec                      | 2 Bytes |

| 271 | Wind Sensor: Störung                          | Ausgang              | L-KÜ  | [1.1] DPT_Switch                               | 1 Bit   |

| 272 | Wind Sensor: Messwert [m/s]                   | Ausgang              | L-KÜ  | [9.5] DPT_Value_Wsp                            | 2 Bytes |

| 273 | Wind Sensor: Messwert [Beaufort]              | Ausgang              | L-KÜ  | [20.014] DPT_Be-<br>aufort_Wind<br>Force_Scale | 1 Byte  |

| 274 | Wind Sensor: Messwert Max Anfrage             | Eingang              | -SK-  | [1.017] DPT_Trigger                            | 1 Bit   |

| 275 | Wind Sensor: Messwert Maximal [m/s]           | Ausgang              | L-KÜ  | [9.5] DPT_Value_Wsp                            | 2 Bytes |

| 276 | Wind Sensor: Messwert Maximal [Beaufort]      | Ausgang              | L-KÜ  | [20.014] DPT_Be-<br>aufort_Wind<br>Force_Scale | 1 Byte  |

| 277 | Wind Sensor: Messwert Max Reset               | Eingang              | -SK-  | [1.017] DPT_Trigger                            | 1 Bit   |

| 281 | Wind Grenzwert 1: Absolutwert                 | Eingang /<br>Ausgang | LSKÜ  | [9.5] DPT_Value_Wsp                            | 2 Bytes |

| 282 | Wind Grenzwert 1: (1:+   0:-)                 | Eingang              | -SK-  | [1.1] DPT_Switch                               | 1 Bit   |

| 283 | Wind Grenzwert 1: Verzögerung von 0 auf 1     | Eingang              | -SK-  | [7.5] DPT_TimePeriod-<br>Sec                   | 2 Bytes |

| 284 | Wind Grenzwert 1: Verzögerung von 1 auf 0     | Eingang              | -SK-  | [7.5] DPT_TimePeriod-<br>Sec                   | 2 Bytes |

| 285 | Wind Grenzwert 1: Schaltausgang               | Ausgang              | L-KÜ  | [1.1] DPT_Switch                               | 1 Bit   |

| 286 | Wind Grenzwert 1: Schaltausgang<br>Sperre     | Eingang              | -SK-  | [1.1] DPT_Switch                               | 1 Bit   |

| 287 | Wind Grenzwert 2: Absolutwert                 | Eingang /<br>Ausgang | LSKÜ  | [9.5] DPT_Value_Wsp                            | 2 Bytes |

| 288 | Wind Grenzwert 2: (1:+   0:-)                 | Eingang              | -SK-  | [1.1] DPT_Switch                               | 1 Bit   |

| Nr.  | Text                                      | Funktion             | Flags | DPT Typ                      | Größe       |

|------|-------------------------------------------|----------------------|-------|------------------------------|-------------|

| 289  | Wind Grenzwert 2: Verzögerung von 0 auf 1 | Eingang              | -SK-  | [7.5] DPT_TimePeriod-<br>Sec | 2 Bytes     |

| 290  | Wind Grenzwert 2: Verzögerung von 1 auf 0 | Eingang              | -SK-  | [7.5] DPT_TimePeriod-<br>Sec | 2 Bytes     |

| 291  | Wind Grenzwert 2: Schaltausgang           | Ausgang              | L-KÜ  | [1.1] DPT_Switch             | 1 Bit       |

| 292  | Wind Grenzwert 2: Schaltausgang<br>Sperre | Eingang              | -SK-  | [1.1] DPT_Switch             | 1 Bit       |

| 293  | Wind Grenzwert 3: Absolutwert             | Eingang /<br>Ausgang | LSKÜ  | [9.5] DPT_Value_Wsp          | 2 Bytes     |

| 294  | Wind Grenzwert 3: (1:+   0:-)             | Eingang              | -SK-  | [1.1] DPT_Switch             | 1 Bit       |

| 295  | Wind Grenzwert 3: Verzögerung von 0 auf 1 | Eingang              | -SK-  | [7.5] DPT_TimePeriod-<br>Sec | 2 Bytes     |

| 296  | Wind Grenzwert 3: Verzögerung von 1 auf 0 | Eingang              | -SK-  | [7.5] DPT_TimePeriod-<br>Sec | 2 Bytes     |

| 297  | Wind Grenzwert 3: Schaltausgang           | Ausgang              | L-KÜ  | [1.1] DPT_Switch             | 1 Bit       |

| 298  | Wind Grenzwert 3: Schaltausgang<br>Sperre | Eingang              | -SK-  | [1.1] DPT_Switch             | 1 Bit       |

| 299  | Wind Grenzwert 4: Absolutwert             | Eingang /<br>Ausgang | LSKÜ  | [9.5] DPT_Value_Wsp          | 2 Bytes     |

| 300  | Wind Grenzwert 4: (1:+   0:-)             | Eingang              | -SK-  | [1.1] DPT_Switch             | 1 Bit       |

| 301  | Wind Grenzwert 4: Verzögerung von 0 auf 1 | Eingang              | -SK-  | [7.5] DPT_TimePeriod-<br>Sec | 2 Bytes     |

| 302  | Wind Grenzwert 4: Verzögerung von 1 auf 0 | Eingang              | -SK-  | [7.5] DPT_TimePeriod-<br>Sec | 2 Bytes     |

| 303  | Wind Grenzwert 4: Schaltausgang           | Ausgang              | L-KÜ  | [1.1] DPT_Switch             | 1 Bit       |

| 304  | Wind Grenzwert 4: Schaltausgang<br>Sperre | Eingang              | -SK-  | [1.1] DPT_Switch             | 1 Bit       |

| 1141 | Berechner 1: Eingang E1                   | Eingang              | LSKÜ  |                              | 4 Bytes     |

| 1142 | Berechner 1: Eingang E2                   | Eingang              | LSKÜ  |                              | 4 Bytes     |

| 1143 | Berechner 1: Eingang E3                   | Eingang              | LSKÜ  |                              | 4 Bytes     |

| 1144 | Berechner 1: Ausgang A1                   | Ausgang              | L-KÜ  |                              | 4 Bytes     |

| 1145 | Berechner 1: Ausgang A2                   | Ausgang              | L-KÜ  |                              | 4 Bytes     |

| 1146 | Berechner 1: Bedingungstext               | Ausgang              | L-KÜ  | [16.0] DPT_String_AS-<br>CII | 14<br>Bytes |

| 1147 | Berechner 1: Überwachungsstatus           | Ausgang              | L-KÜ  | [1.1] DPT_Switch             | 1 Bit       |

| 1148 | Berechner 1: Sperre (1 : Sperren)         | Eingang              | -SK-  | [1.1] DPT_Switch             | 1 Bit       |

| 1149 | Berechner 2: Eingang E1                   | Eingang              | LSKÜ  |                              | 4 Bytes     |

| 1150 | Berechner 2: Eingang E2                   | Eingang              | LSKÜ  |                              | 4 Bytes     |

| 1151 | Berechner 2: Eingang E3                   | Eingang              | LSKÜ  |                              | 4 Bytes     |

| 1152 | Berechner 2: Ausgang A1                   | Ausgang              | L-KÜ  |                              | 4 Bytes     |

| 1153 | Berechner 2: Ausgang A2                   | Ausgang              | L-KÜ  |                              | 4 Bytes     |

| 1154 | Berechner 2: Bedingungstext               | Ausgang              | L-KÜ  | [16.0] DPT_String_AS-<br>CII | 14<br>Bytes |

| 1155 | Berechner 2: Überwachungsstatus           | Ausgang              | L-KÜ  | [1.1] DPT_Switch             | 1 Bit       |

| 1156 | Berechner 2: Sperre (1 : Sperren)         | Eingang              | -SK-  | [1.1] DPT_Switch             | 1 Bit       |

| 1157 | Berechner 3: Eingang E1                   | Eingang              | LSKÜ  |                              | 4 Bytes     |

| Nr.  | Text                              | Funktion | Flags | DPT Typ                      | Größe       |

|------|-----------------------------------|----------|-------|------------------------------|-------------|

| 1158 | Berechner 3: Eingang E2           | Eingang  | LSKÜ  | 7.                           | 4 Bytes     |

| 1159 | Berechner 3: Eingang E3           | Eingang  | LSKÜ  |                              | 4 Bytes     |

| 1160 | Berechner 3: Ausgang A1           | Ausgang  | L-KÜ  |                              | 4 Bytes     |

| 1161 | Berechner 3: Ausgang A2           | Ausgang  | L-KÜ  |                              | 4 Bytes     |

| 1162 | Berechner 3: Bedingungstext       | Ausgang  | L-KÜ  | [16.0] DPT_String_AS-<br>CII | 14<br>Bytes |

| 1163 | Berechner 3: Überwachungsstatus   | Ausgang  | L-KÜ  | [1.1] DPT_Switch             | 1 Bit       |

| 1164 | Berechner 3: Sperre (1 : Sperren) | Eingang  | -SK-  | [1.1] DPT_Switch             | 1 Bit       |

| 1165 | Berechner 4: Eingang E1           | Eingang  | LSKÜ  |                              | 4 Bytes     |

| 1166 | Berechner 4: Eingang E2           | Eingang  | LSKÜ  |                              | 4 Bytes     |

| 1167 | Berechner 4: Eingang E3           | Eingang  | LSKÜ  |                              | 4 Bytes     |

| 1168 | Berechner 4: Ausgang A1           | Ausgang  | L-KÜ  |                              | 4 Bytes     |

| 1169 | Berechner 4: Ausgang A2           | Ausgang  | L-KÜ  |                              | 4 Bytes     |

| 1170 | Berechner 4: Bedingungstext       | Ausgang  | L-KÜ  | [16.0] DPT_String_AS-<br>CII | 14<br>Bytes |

| 1171 | Berechner 4: Überwachungsstatus   | Ausgang  | L-KÜ  | [1.1] DPT_Switch             | 1 Bit       |

| 1172 | Berechner 4: Sperre (1 : Sperren) | Eingang  | -SK-  | [1.1] DPT_Switch             | 1 Bit       |

| 1173 | Berechner 5: Eingang E1           | Eingang  | LSKÜ  |                              | 4 Bytes     |

| 1174 | Berechner 5: Eingang E2           | Eingang  | LSKÜ  |                              | 4 Bytes     |

| 1175 | Berechner 5: Eingang E3           | Eingang  | LSKÜ  |                              | 4 Bytes     |

| 1176 | Berechner 5: Ausgang A1           | Ausgang  | L-KÜ  |                              | 4 Bytes     |

| 1177 | Berechner 5: Ausgang A2           | Ausgang  | L-KÜ  |                              | 4 Bytes     |

| 1178 | Berechner 5: Bedingungstext       | Ausgang  | L-KÜ  | [16.0] DPT_String_AS-<br>CII | 14<br>Bytes |

| 1179 | Berechner 5: Überwachungsstatus   | Ausgang  | L-KÜ  | [1.1] DPT_Switch             | 1 Bit       |

| 1180 | Berechner 5: Sperre (1 : Sperren) | Eingang  | -SK-  | [1.1] DPT_Switch             | 1 Bit       |

| 1181 | Berechner 6: Eingang E1           | Eingang  | LSKÜ  |                              | 4 Bytes     |

| 1182 | Berechner 6: Eingang E2           | Eingang  | LSKÜ  |                              | 4 Bytes     |

| 1183 | Berechner 6: Eingang E3           | Eingang  | LSKÜ  |                              | 4 Bytes     |

| 1184 | Berechner 6: Ausgang A1           | Ausgang  | L-KÜ  |                              | 4 Bytes     |

| 1185 | Berechner 6: Ausgang A2           | Ausgang  | L-KÜ  |                              | 4 Bytes     |

| 1186 | Berechner 6: Bedingungstext       | Ausgang  | L-KÜ  | [16.0] DPT_String_AS-<br>CII | 14<br>Bytes |

| 1187 | Berechner 6: Überwachungsstatus   | Ausgang  | L-KÜ  | [1.1] DPT_Switch             | 1 Bit       |

| 1188 | Berechner 6: Sperre (1 : Sperren) | Eingang  | -SK-  | [1.1] DPT_Switch             | 1 Bit       |

| 1189 | Berechner 7: Eingang E1           | Eingang  | LSKÜ  |                              | 4 Bytes     |

| 1190 | Berechner 7: Eingang E2           | Eingang  | LSKÜ  |                              | 4 Bytes     |

| 1191 | Berechner 7: Eingang E3           | Eingang  | LSKÜ  |                              | 4 Bytes     |

| 1192 | Berechner 7: Ausgang A1           | Ausgang  | L-KÜ  |                              | 4 Bytes     |

| 1193 | Berechner 7: Ausgang A2           | Ausgang  | L-KÜ  |                              | 4 Bytes     |

| 1194 | Berechner 7: Bedingungstext       | Ausgang  | L-KÜ  | [16.0] DPT_String_AS-<br>CII | 14<br>Bytes |

| 1195 | Berechner 7: Überwachungsstatus   | Ausgang  | L-KÜ  | [1.1] DPT_Switch             | 1 Bit       |

| 1196 | Berechner 7: Sperre (1 : Sperren) | Eingang  | -SK-  | [1.1] DPT_Switch             | 1 Bit       |

| Nr.  | Text                              | Funktion | Flags | DPT Typ               | Größe   |

|------|-----------------------------------|----------|-------|-----------------------|---------|

| 1197 | Berechner 8: Eingang E1           | Eingang  | LSKÜ  |                       | 4 Bytes |

| 1198 | Berechner 8: Eingang E2           | Eingang  | LSKÜ  |                       | 4 Bytes |

| 1199 | Berechner 8: Eingang E3           | Eingang  | LSKÜ  |                       | 4 Bytes |

| 1200 | Berechner 8: Ausgang A1           | Ausgang  | L-KÜ  |                       | 4 Bytes |

| 1201 | Berechner 8: Ausgang A2           | Ausgang  | L-KÜ  |                       | 4 Bytes |

| 1202 | Berechner 8: Bedingungstext       | Ausgang  | L-KÜ  | [16.0] DPT_String_AS- | 14      |

| 1203 | Berechner 8: Überwachungsstatus   | A        | L-KÜ  | [1.1] DPT Switch      | Bytes   |

|      | •                                 | Ausgang  |       |                       | 1 Bit   |

| 1204 | Berechner 8: Sperre (1 : Sperren) | Eingang  | -SK-  | [1.1] DPT_Switch      | 1 Bit   |

| 1391 | Logikeingang 1                    | Eingang  | -SK-  | [1.2] DPT_Bool        | 1 Bit   |

| 1392 | Logikeingang 2                    | Eingang  | -SK-  | [1.2] DPT_Bool        | 1 Bit   |

| 1393 | Logikeingang 3                    | Eingang  | -SK-  | [1.2] DPT_Bool        | 1 Bit   |

| 1394 | Logikeingang 4                    | Eingang  | -SK-  | [1.2] DPT_Bool        | 1 Bit   |

| 1395 | Logikeingang 5                    | Eingang  | -SK-  | [1.2] DPT_Bool        | 1 Bit   |

| 1396 | Logikeingang 6                    | Eingang  | -SK-  | [1.2] DPT_Bool        | 1 Bit   |

| 1397 | Logikeingang 7                    | Eingang  | -SK-  | [1.2] DPT_Bool        | 1 Bit   |

| 1398 | Logikeingang 8                    | Eingang  | -SK-  | [1.2] DPT_Bool        | 1 Bit   |

| 1399 | Logikeingang 9                    | Eingang  | -SK-  | [1.2] DPT_Bool        | 1 Bit   |

| 1400 | Logikeingang 10                   | Eingang  | -SK-  | [1.2] DPT_Bool        | 1 Bit   |

| 1401 | Logikeingang 11                   | Eingang  | -SK-  | [1.2] DPT_Bool        | 1 Bit   |

| 1402 | Logikeingang 12                   | Eingang  | -SK-  | [1.2] DPT_Bool        | 1 Bit   |

| 1403 | Logikeingang 13                   | Eingang  | -SK-  | [1.2] DPT_Bool        | 1 Bit   |

| 1404 | Logikeingang 14                   | Eingang  | -SK-  | [1.2] DPT_Bool        | 1 Bit   |

| 1405 | Logikeingang 15                   | Eingang  | -SK-  | [1.2] DPT_Bool        | 1 Bit   |

| 1406 | Logikeingang 16                   | Eingang  | -SK-  | [1.2] DPT_Bool        | 1 Bit   |

| 1411 | UND Logik 1: 1 Bit Schaltausgang  | Ausgang  | L-KÜ  | [1.2] DPT_Bool        | 1 Bit   |

| 1412 | UND Logik 1: 8 Bit Ausgang A      | Ausgang  | L-KÜ  |                       | 1 Byte  |

| 1413 | UND Logik 1: 8 Bit Ausgang B      | Ausgang  | L-KÜ  |                       | 1 Byte  |

| 1414 | UND Logik 1: Sperre               | Eingang  | -SK-  | [1.1] DPT_Switch      | 1 Bit   |

| 1415 | UND Logik 2: 1 Bit Schaltausgang  | Ausgang  | L-KÜ  | [1.2] DPT_Bool        | 1 Bit   |

| 1416 | UND Logik 2: 8 Bit Ausgang A      | Ausgang  | L-KÜ  |                       | 1 Byte  |

| 1417 | UND Logik 2: 8 Bit Ausgang B      | Ausgang  | L-KÜ  |                       | 1 Byte  |

| 1418 | UND Logik 2: Sperre               | Eingang  | -SK-  | [1.1] DPT_Switch      | 1 Bit   |

| 1419 | UND Logik 3: 1 Bit Schaltausgang  | Ausgang  | L-KÜ  | [1.2] DPT_Bool        | 1 Bit   |

| 1420 | UND Logik 3: 8 Bit Ausgang A      | Ausgang  | L-KÜ  |                       | 1 Byte  |

| 1421 | UND Logik 3: 8 Bit Ausgang B      | Ausgang  | L-KÜ  |                       | 1 Byte  |

| 1422 | UND Logik 3: Sperre               | Eingang  | -SK-  | [1.1] DPT_Switch      | 1 Bit   |

| 1423 | UND Logik 4: 1 Bit Schaltausgang  | Ausgang  | L-KÜ  | [1.2] DPT_Bool        | 1 Bit   |

| 1424 | UND Logik 4: 8 Bit Ausgang A      | Ausgang  | L-KÜ  |                       | 1 Byte  |

| 1425 | UND Logik 4: 8 Bit Ausgang B      | Ausgang  | L-KÜ  |                       | 1 Byte  |

| 1426 | UND Logik 4: Sperre               | Eingang  | -SK-  | [1.1] DPT_Switch      | 1 Bit   |

| 1427 | UND Logik 5: 1 Bit Schaltausgang  | Ausgang  | L-KÜ  | [1.2] DPT_Bool        | 1 Bit   |

| 1428 | UND Logik 5: 8 Bit Ausgang A      | Ausgang  | L-KÜ  |                       | 1 Byte  |

| 1429UND Logik 5: 8 Bit Ausgang BAusgangL-KÜ1430UND Logik 5: SperreEingang-SK-[1.1] DPT_Switch1431UND Logik 6: 1 Bit SchaltausgangAusgangL-KÜ[1.2] DPT_Bool1432UND Logik 6: 8 Bit Ausgang AAusgangL-KÜL-KÜ1433UND Logik 6: 8 Bit Ausgang BAusgangL-KÜL-KÜ1434UND Logik 6: SperreEingang-SK-[1.1] DPT_Switch1435UND Logik 7: 1 Bit SchaltausgangAusgangL-KÜ[1.2] DPT_Bool1436UND Logik 7: 8 Bit Ausgang AAusgangL-KÜ[1.1] DPT_Switch1437UND Logik 7: 8 Bit Ausgang BAusgangL-KÜ[1.1] DPT_Switch1438UND Logik 8: 1 Bit SchaltausgangAusgangL-KÜ[1.2] DPT_Bool1440UND Logik 8: 8 Bit Ausgang AAusgangL-KÜ[1.2] DPT_Bool1441UND Logik 8: 8 Bit Ausgang BAusgangL-KÜ[1.2] DPT_Switch1442UND Logik 8: SperreEingang-SK-[1.1] DPT_Switch1443ODER Logik 1: 1 Bit SchaltausgangAusgangL-KÜ[1.2] DPT_Bool1444ODER Logik 1: 8 Bit Ausgang BAusgangL-KÜ1445ODER Logik 1: 8 Bit Ausgang BAusgangL-KÜ1446ODER Logik 1: SperreEingang-SK-[1.1] DPT_Switch1447ODER Logik 2: 1 Bit SchaltausgangAusgangL-KÜ[1.2] DPT_Bool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 Byte 1 Bit 1 Bit 1 Byte 1 Byte 1 Byte 1 Bit 1 Bit 1 Byte |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| 1431 UND Logik 6: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool 1432 UND Logik 6: 8 Bit Ausgang A Ausgang L-KÜ 1433 UND Logik 6: 8 Bit Ausgang B Ausgang L-KÜ 1434 UND Logik 6: Sperre Eingang -SK- [1.1] DPT_Switch 1435 UND Logik 7: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool 1436 UND Logik 7: 8 Bit Ausgang A Ausgang L-KÜ 1437 UND Logik 7: 8 Bit Ausgang B Ausgang L-KÜ 1438 UND Logik 7: Sperre Eingang -SK- [1.1] DPT_Switch 1439 UND Logik 8: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool 1440 UND Logik 8: 8 Bit Ausgang A Ausgang L-KÜ [1.2] DPT_Bool 1441 UND Logik 8: 8 Bit Ausgang B Ausgang L-KÜ 1442 UND Logik 8: 8 Bit Ausgang B Ausgang L-KÜ 1443 ODER Logik 1: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool 1444 ODER Logik 1: 8 Bit Ausgang A Ausgang L-KÜ 1445 ODER Logik 1: 8 Bit Ausgang B Ausgang L-KÜ 1446 ODER Logik 1: Sperre Eingang -SK- [1.1] DPT_Switch 1447 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1447 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1-KÜ 1-LI] DPT_Switch 1-KÜ 1-LI] DPT_Switch 1-KÜ 1-LI] DPT_Switch 1-KÜ 1-LI] DPT_Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1 Bit 1 Byte 1 Byte 1 Bit 1 Bit 1 Bit 1 Bit                |

| 1432         UND Logik 6: 8 Bit Ausgang A         Ausgang L-KÜ           1433         UND Logik 6: 8 Bit Ausgang B         Ausgang L-KÜ           1434         UND Logik 6: Sperre         Eingang -SK- [1.1] DPT_Switch           1435         UND Logik 7: 1 Bit Schaltausgang A         Ausgang L-KÜ [1.2] DPT_Bool           1436         UND Logik 7: 8 Bit Ausgang A         Ausgang L-KÜ           1437         UND Logik 7: 8 Bit Ausgang B         Ausgang L-KÜ           1438         UND Logik 7: Sperre         Eingang -SK- [1.1] DPT_Switch           1439         UND Logik 8: 1 Bit Schaltausgang A         Ausgang L-KÜ [1.2] DPT_Bool           1440         UND Logik 8: 8 Bit Ausgang A         Ausgang L-KÜ [1.2] DPT_Bool           1441         UND Logik 8: 8 Bit Ausgang B         Ausgang L-KÜ [1.2] DPT_Switch           1443         ODER Logik 1: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool           1444         ODER Logik 1: 8 Bit Ausgang A Ausgang L-KÜ [1.2] DPT_Bool           1445         ODER Logik 1: 8 Bit Ausgang B Ausgang L-KÜ [1.2] DPT_Switch           1445         ODER Logik 1: 8 Bit Ausgang B Ausgang L-KÜ [1.1] DPT_Switch           1446         ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool                                                                                                                                                                                                                                                                                                       | 1 Byte 1 Byte 1 Bit 1 Bit 1 Byte                           |

| 1433         UND Logik 6: 8 Bit Ausgang B         Ausgang         L-KÜ           1434         UND Logik 6: Sperre         Eingang         -SK-         [1.1] DPT_Switch           1435         UND Logik 7: 1 Bit Schaltausgang         Ausgang         L-KÜ         [1.2] DPT_Bool           1436         UND Logik 7: 8 Bit Ausgang A         Ausgang         L-KÜ           1437         UND Logik 7: 8 Bit Ausgang B         Ausgang         L-KÜ           1438         UND Logik 7: Sperre         Eingang         SK-         [1.1] DPT_Switch           1439         UND Logik 8: 1 Bit Schaltausgang         Ausgang         L-KÜ         [1.2] DPT_Bool           1440         UND Logik 8: 8 Bit Ausgang A         Ausgang         L-KÜ           1441         UND Logik 8: 8 Bit Ausgang B         Ausgang         L-KÜ           1442         UND Logik 8: Sperre         Eingang         -SK-         [1.1] DPT_Switch           1443         ODER Logik 1: 1 Bit Schaltausgang         Ausgang         L-KÜ         [1.2] DPT_Bool           1444         ODER Logik 1: 8 Bit Ausgang B         Ausgang         L-KÜ         [1.1] DPT_Switch           1445         ODER Logik 1: 8 Bit Ausgang B         Ausgang         L-KÜ         [1.1] DPT_Switch           1446         ODER L                                                                                                                                                                                                                                                                            | 1 Byte 1 Bit 1 Bit 1 Byte                                  |

| 1434 UND Logik 6: Sperre Eingang -SK- [1.1] DPT_Switch 1435 UND Logik 7: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool 1436 UND Logik 7: 8 Bit Ausgang A Ausgang L-KÜ 1437 UND Logik 7: 8 Bit Ausgang B Ausgang L-KÜ 1438 UND Logik 7: Sperre Eingang -SK- [1.1] DPT_Switch 1439 UND Logik 8: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool 1440 UND Logik 8: 8 Bit Ausgang A Ausgang L-KÜ 1441 UND Logik 8: 8 Bit Ausgang B Ausgang L-KÜ 1442 UND Logik 8: Sperre Eingang -SK- [1.1] DPT_Switch 1443 ODER Logik 1: 1 Bit Schaltausgang Ausgang L-KÜ 1444 ODER Logik 1: 8 Bit Ausgang A Ausgang L-KÜ 1445 ODER Logik 1: 8 Bit Ausgang B Ausgang L-KÜ 1446 ODER Logik 1: Sperre Eingang -SK- [1.1] DPT_Switch 1447 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1447 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1447 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1447 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1448 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1449 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1440 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1441 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1442 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1443 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1444 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1445 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1446 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1447 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1448 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ 1449 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ | 1 Bit<br>1 Bit<br>1 Byte                                   |

| 1435         UND Logik 7: 1 Bit Schaltausgang         Ausgang         L-KÜ         [1.2] DPT_Bool           1436         UND Logik 7: 8 Bit Ausgang A         Ausgang         L-KÜ           1437         UND Logik 7: 8 Bit Ausgang B         Ausgang         L-KÜ           1438         UND Logik 7: Sperre         Eingang         -SK-         [1.1] DPT_Switch           1439         UND Logik 8: 1 Bit Schaltausgang         Ausgang         L-KÜ         [1.2] DPT_Bool           1440         UND Logik 8: 8 Bit Ausgang A         Ausgang         L-KÜ           1441         UND Logik 8: 8 Bit Ausgang B         Ausgang         L-KÜ           1442         UND Logik 8: Sperre         Eingang         -SK-         [1.1] DPT_Switch           1443         ODER Logik 1: 1 Bit Schaltausgang         Ausgang         L-KÜ         [1.2] DPT_Bool           1444         ODER Logik 1: 8 Bit Ausgang B         Ausgang         L-KÜ         [1.1] DPT_Switch           1445         ODER Logik 1: 8 Bit Ausgang B         Ausgang         L-KÜ         [1.1] DPT_Switch           1446         ODER Logik 2: 1 Bit Schaltausgang         Ausgang         L-KÜ         [1.1] DPT_Switch                                                                                                                                                                                                                                                                                                                                                                            | 1 Bit<br>1 Byte                                            |

| 1436         UND Logik 7: 8 Bit Ausgang A         Ausgang L-KÜ           1437         UND Logik 7: 8 Bit Ausgang B         Ausgang L-KÜ           1438         UND Logik 7: Sperre         Eingang -SK- [1.1] DPT_Switch           1439         UND Logik 8: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool           1440         UND Logik 8: 8 Bit Ausgang A Ausgang L-KÜ           1441         UND Logik 8: 8 Bit Ausgang B Ausgang L-KÜ           1442         UND Logik 8: Sperre Eingang -SK- [1.1] DPT_Switch           1443         ODER Logik 1: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool           1444         ODER Logik 1: 8 Bit Ausgang A Ausgang L-KÜ           1445         ODER Logik 1: 8 Bit Ausgang B Ausgang L-KÜ           1446         ODER Logik 1: Sperre Eingang -SK- [1.1] DPT_Switch           1447         ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 Byte                                                     |

| 1437 UND Logik 7: 8 Bit Ausgang B Ausgang L-KÜ 1438 UND Logik 7: Sperre Eingang -SK- [1.1] DPT_Switch 1439 UND Logik 8: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool 1440 UND Logik 8: 8 Bit Ausgang A Ausgang L-KÜ 1441 UND Logik 8: 8 Bit Ausgang B Ausgang L-KÜ 1442 UND Logik 8: Sperre Eingang -SK- [1.1] DPT_Switch 1443 ODER Logik 1: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool 1444 ODER Logik 1: 8 Bit Ausgang B Ausgang L-KÜ 1445 ODER Logik 1: 8 Bit Ausgang B Ausgang L-KÜ 1446 ODER Logik 1: Sperre Eingang -SK- [1.1] DPT_Switch 1447 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | - '                                                        |

| 1438 UND Logik 7: Sperre Eingang -SK- [1.1] DPT_Switch 1439 UND Logik 8: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool 1440 UND Logik 8: 8 Bit Ausgang A Ausgang L-KÜ 1441 UND Logik 8: 8 Bit Ausgang B Ausgang L-KÜ 1442 UND Logik 8: Sperre Eingang -SK- [1.1] DPT_Switch 1443 ODER Logik 1: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool 1444 ODER Logik 1: 8 Bit Ausgang A Ausgang L-KÜ 1445 ODER Logik 1: 8 Bit Ausgang B Ausgang L-KÜ 1446 ODER Logik 1: Sperre Eingang -SK- [1.1] DPT_Switch 1447 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4.5                                                        |

| 1439 UND Logik 8: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool  1440 UND Logik 8: 8 Bit Ausgang A Ausgang L-KÜ  1441 UND Logik 8: 8 Bit Ausgang B Ausgang L-KÜ  1442 UND Logik 8: Sperre Eingang -SK- [1.1] DPT_Switch  1443 ODER Logik 1: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool  1444 ODER Logik 1: 8 Bit Ausgang A Ausgang L-KÜ  1445 ODER Logik 1: 8 Bit Ausgang B Ausgang L-KÜ  1446 ODER Logik 1: Sperre Eingang -SK- [1.1] DPT_Switch  1447 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 Byte                                                     |

| 1440 UND Logik 8: 8 Bit Ausgang A Ausgang L-KÜ  1441 UND Logik 8: 8 Bit Ausgang B Ausgang L-KÜ  1442 UND Logik 8: Sperre Eingang -SK- [1.1] DPT_Switch  1443 ODER Logik 1: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool  1444 ODER Logik 1: 8 Bit Ausgang A Ausgang L-KÜ  1445 ODER Logik 1: 8 Bit Ausgang B Ausgang L-KÜ  1446 ODER Logik 1: Sperre Eingang -SK- [1.1] DPT_Switch  1447 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 Bit                                                      |

| 1441 UND Logik 8: 8 Bit Ausgang B Ausgang L-KÜ  1442 UND Logik 8: Sperre Eingang -SK- [1.1] DPT_Switch  1443 ODER Logik 1: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool  1444 ODER Logik 1: 8 Bit Ausgang A Ausgang L-KÜ  1445 ODER Logik 1: 8 Bit Ausgang B Ausgang L-KÜ  1446 ODER Logik 1: Sperre Eingang -SK- [1.1] DPT_Switch  1447 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 Bit                                                      |

| 1442UND Logik 8: SperreEingang-SK-[1.1] DPT_Switch1443ODER Logik 1: 1 Bit SchaltausgangAusgangL-KÜ[1.2] DPT_Bool1444ODER Logik 1: 8 Bit Ausgang AAusgangL-KÜ1445ODER Logik 1: 8 Bit Ausgang BAusgangL-KÜ1446ODER Logik 1: SperreEingang-SK-[1.1] DPT_Switch1447ODER Logik 2: 1 Bit SchaltausgangAusgangL-KÜ[1.2] DPT_Bool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 Byte                                                     |

| 1443 ODER Logik 1: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool  1444 ODER Logik 1: 8 Bit Ausgang A Ausgang L-KÜ  1445 ODER Logik 1: 8 Bit Ausgang B Ausgang L-KÜ  1446 ODER Logik 1: Sperre Eingang -SK- [1.1] DPT_Switch  1447 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 Byte                                                     |

| 1444ODER Logik 1: 8 Bit Ausgang AAusgang L-KÜ1445ODER Logik 1: 8 Bit Ausgang BAusgang L-KÜ1446ODER Logik 1: SperreEingang -SK- [1.1] DPT_Switch1447ODER Logik 2: 1 Bit SchaltausgangAusgang L-KÜ [1.2] DPT_Bool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 Bit                                                      |

| 1445ODER Logik 1: 8 Bit Ausgang BAusgang L-KÜ1446ODER Logik 1: SperreEingang -SK- [1.1] DPT_Switch1447ODER Logik 2: 1 Bit SchaltausgangAusgang L-KÜ [1.2] DPT_Bool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 Bit                                                      |

| 1445ODER Logik 1: 8 Bit Ausgang BAusgang L-KÜ1446ODER Logik 1: SperreEingang -SK- [1.1] DPT_Switch1447ODER Logik 2: 1 Bit SchaltausgangAusgang L-KÜ [1.2] DPT_Bool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 Byte                                                     |

| 1447 ODER Logik 2: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 Byte                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 Bit                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 Bit                                                      |

| 1448   ODER Logik 2: 8 Bit Ausgang A   Ausgang   L-KÜ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 Byte                                                     |

| 1449 ODER Logik 2: 8 Bit Ausgang B Ausgang L-KÜ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 Byte                                                     |

| 1450 ODER Logik 2: Sperre Eingang -SK- [1.1] DPT_Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 Bit                                                      |

| 1451 ODER Logik 3: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 Bit                                                      |

| 1452 ODER Logik 3: 8 Bit Ausgang A Ausgang L-KÜ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 Byte                                                     |

| 1453 ODER Logik 3: 8 Bit Ausgang B Ausgang L-KÜ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 Byte                                                     |

| 1454 ODER Logik 3: Sperre Eingang -SK- [1.1] DPT_Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 Bit                                                      |

| 1455 ODER Logik 4: 1 Bit Schaltausgang Ausgang L-KÜ [1.2] DPT_Bool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 Bit                                                      |

| 1456 ODER Logik 4: 8 Bit Ausgang A Ausgang L-KÜ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 Byte                                                     |

| 1457 ODER Logik 4: 8 Bit Ausgang B Ausgang L-KÜ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 Byte                                                     |

| 1458 ODER Logik 4: Sperre Eingang -SK- [1.1] DPT_Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 Bit                                                      |